# INTERRUPT INTERFACE OF THE 8088 AND 8086 MICROPROCESSOR

#### INTERRUPT INTERFACE OF THE 8088 AND 8086 MICROPROCESSOR

- 11.1 Interrupt Mechanism, Types and Priority

- 11.2 Interrupt Vector Table

- 11.3 Interrupt Instructions

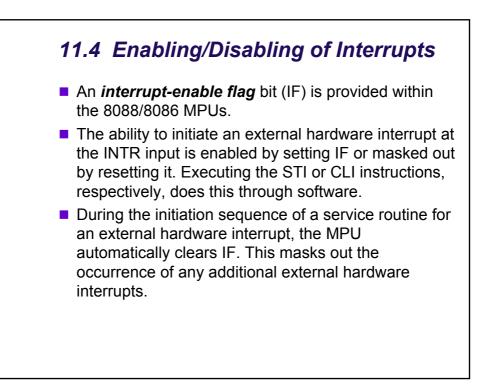

- 11.4 Enabling/Disabling of Interrupts

- 11.5 External Hardware-Interrupt Interface Signals

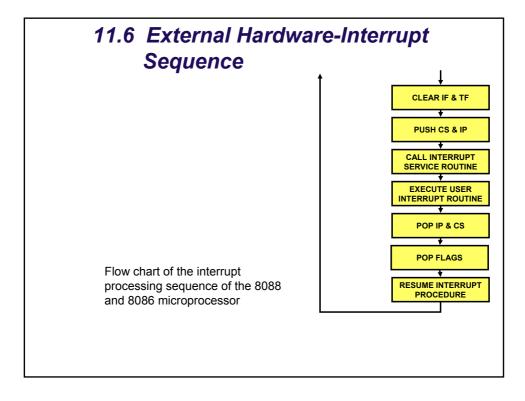

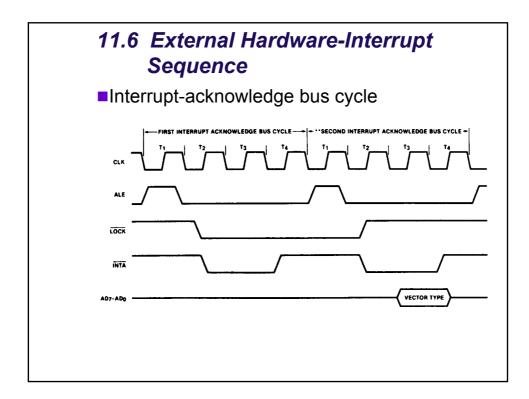

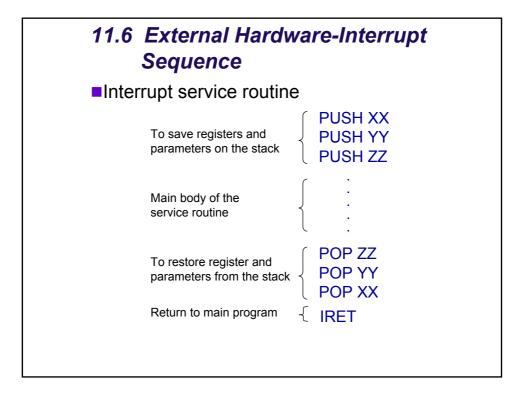

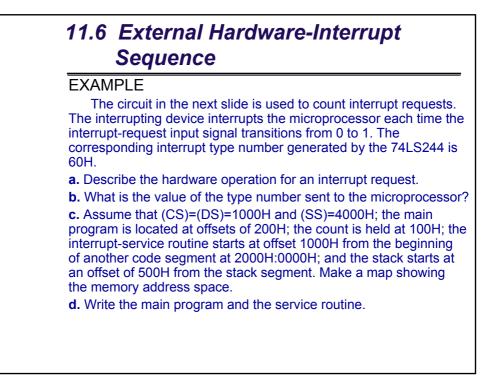

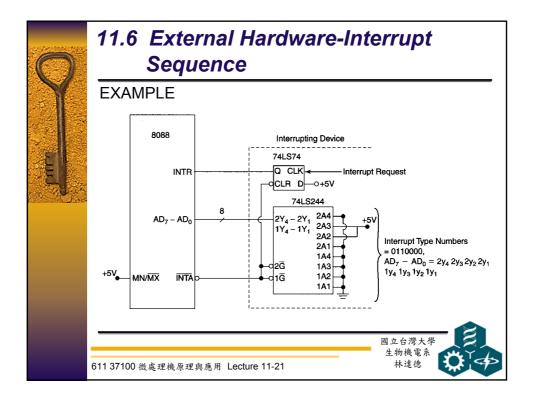

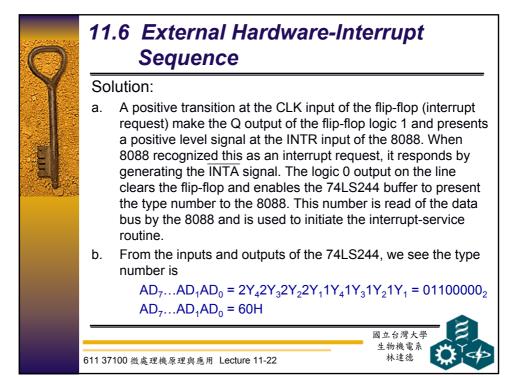

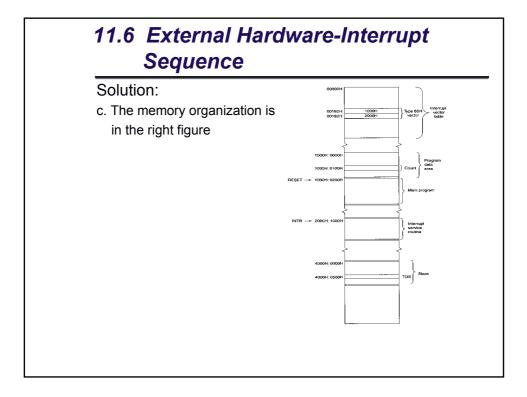

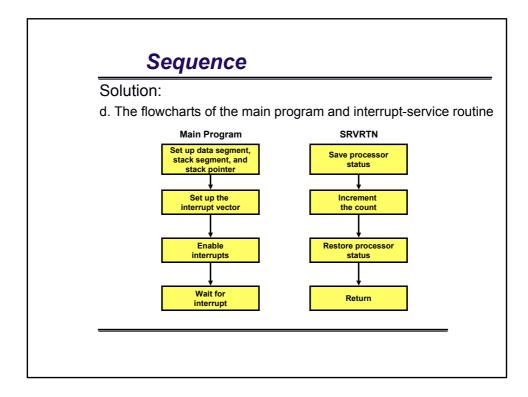

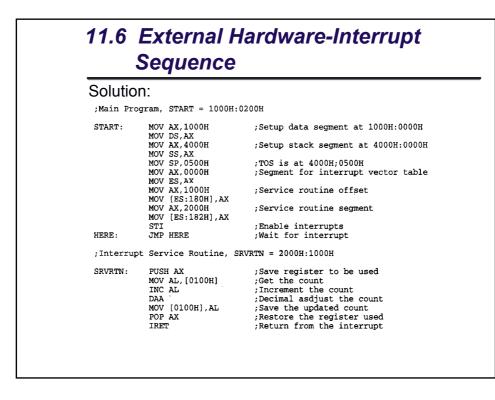

- 11.6 External Hardware-Interrupt Sequence

#### INTERRUP INTERFACE OF THE 8088 AND 8086 MICROPROCESSOR

- 11.7 82C59A Programmable Interrupt Controller

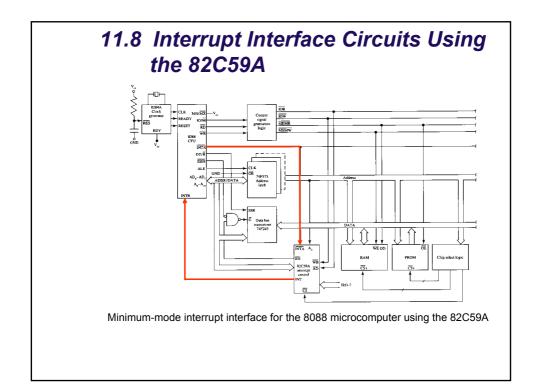

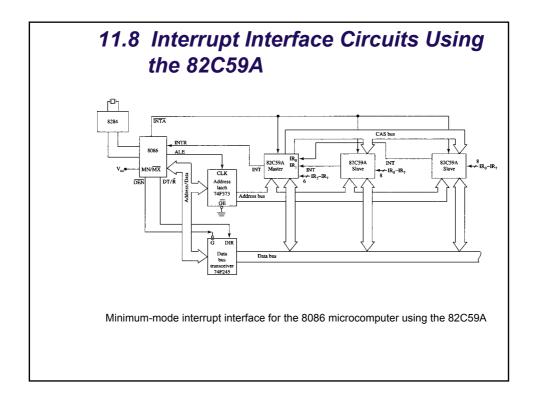

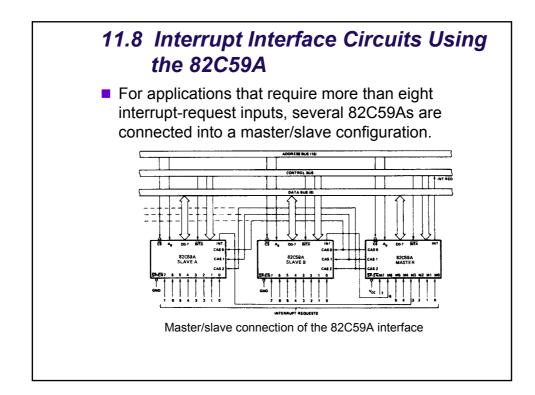

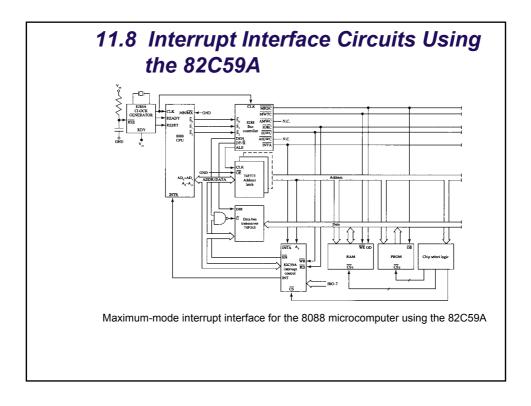

- 11.8 Interrupt Interface Circuits Using the 82C59A

- 11.9 Software Interrupts

- 11.10 Nonmaskable Interrupt

- 11.11 Reset

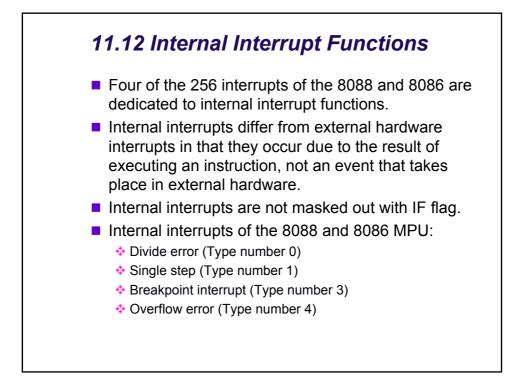

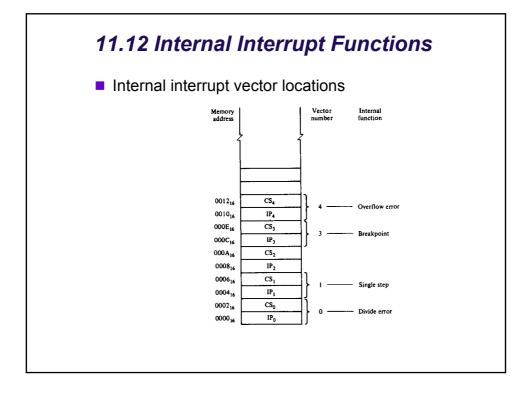

- 11.12 Internal Interrupt Function

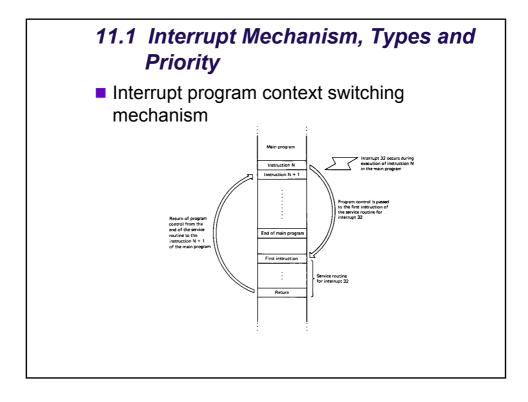

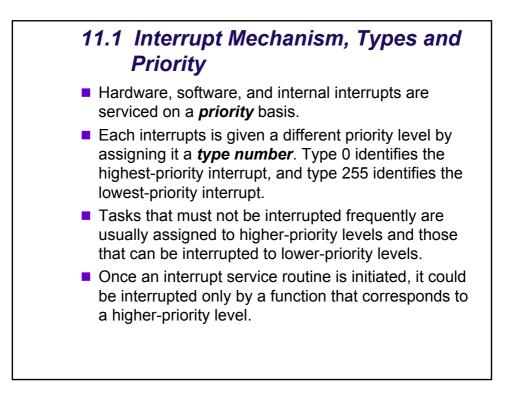

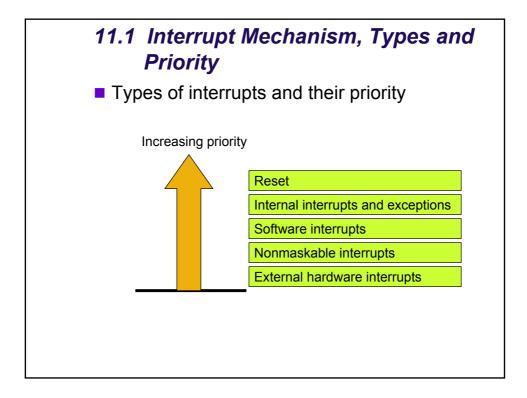

#### 11.1 Interrupt Mechanism, Types and Priority

- Interrupts provide a mechanism for quickly changing program environment. Transfer of program control is initiated by the occurrence of either an event internal to the MPU or an event in its external hardware.

- The section of program to which control is passed is called the *interrupt service routine*.

- The 8088 and 8086 microprocessor are capable of implementing any combination of up to 256 interrupts.

- Interrupts are divided into five groups:

- External hardware interrupts

- Nonmaskable interrupts

- Software interrupts

- Internal interrupts

- reset

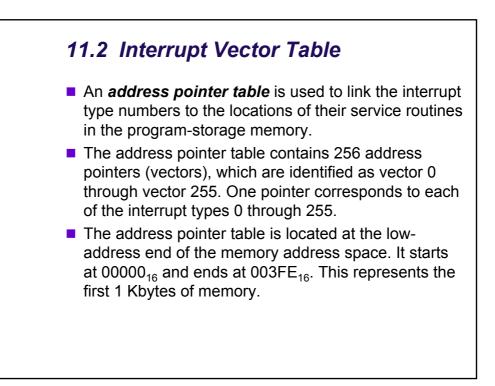

# **11.2 Interrupt Vector Table EXAMPLE** At what address are $CS_{50}$ and $IP_{50}$ stored in memory? **Solution:** Each vector requires four consecutive bytes of memory for storage. Therefore, its address can be found by multiplying the type number by 4. Since $CS_{50}$ and $IP_{50}$ represent the words of the type so interrupt pointer, we get: $Address = 4 \times 50 = 200$ Converting to binary form gives $Address = 1100100_2 = C8_{16}$ Therefore, $IP_{50}$ is stored at $000C8_{16}$ and $CS_{50}$ at $000CA_{16}$ .

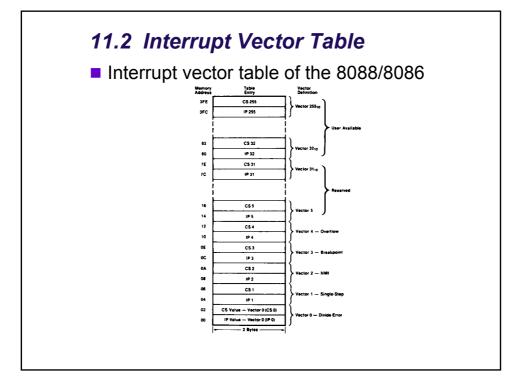

| Mnemonic | Meaning                      | Format | Operation                                                                                                                                                                         | Flags affected |

|----------|------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|

| CLI      | Clear interrupt flag         | CLI    | $0 \rightarrow (IF)$                                                                                                                                                              | IF             |

| STI      | Set interrupt flag           | STI    | $1 \rightarrow (IF)$                                                                                                                                                              | IF             |

| INT n    | Type n software<br>interrupt | INT n  | $      (Flags) \rightarrow ((SP)-2) \\ 0 \rightarrow TF, IF \\ (CS) \rightarrow ((SP) - 4) \\ (2+4xn) \rightarrow (CS) \\ (IP) \rightarrow ((SP) - 6) \\ (4xn) \rightarrow (IP) $ | TF, IF         |

| IRET     | Interrupt return             | IRET   | $\begin{array}{l} ((SP)) \rightarrow (IP) \\ ((SP)+2) \rightarrow (CS) \\ ((SP)+4) \rightarrow (Flags) \\ (SP) + 6 \rightarrow (SP) \end{array}$                                  | All            |

| INTO     | Interrupt on overflow        | INTO   | INT 4 steps                                                                                                                                                                       | TF, IF         |

| HLT      | Halt                         | HLT    | Wait for an external interrupt or reset to occur                                                                                                                                  | None           |

| WAIT     | Wait                         | WAIT   | Wait for TEST input to go active                                                                                                                                                  |                |

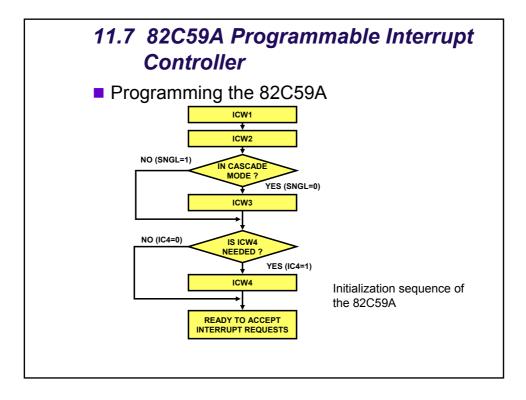

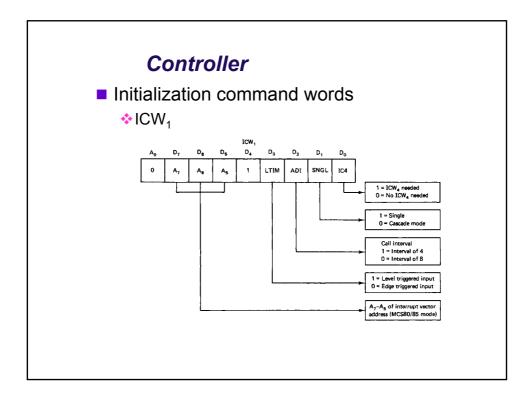

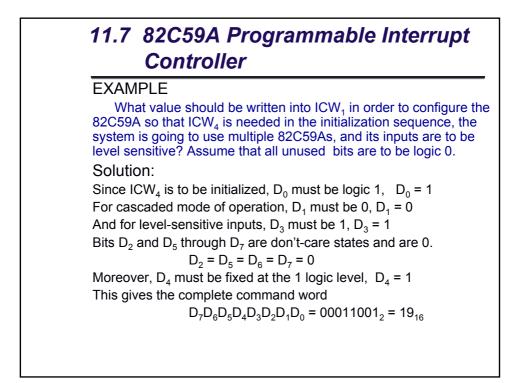

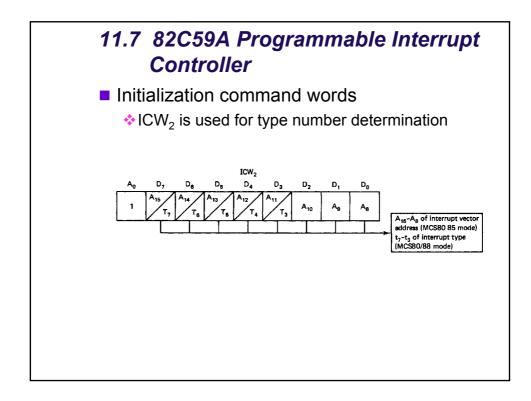

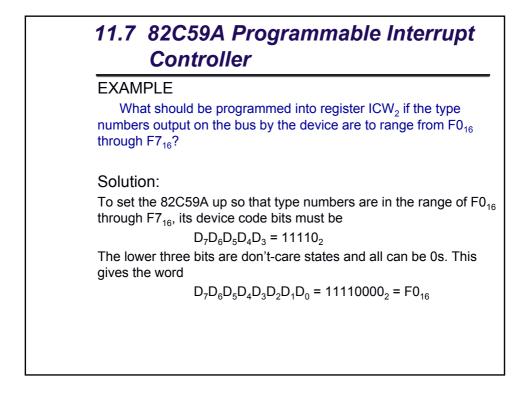

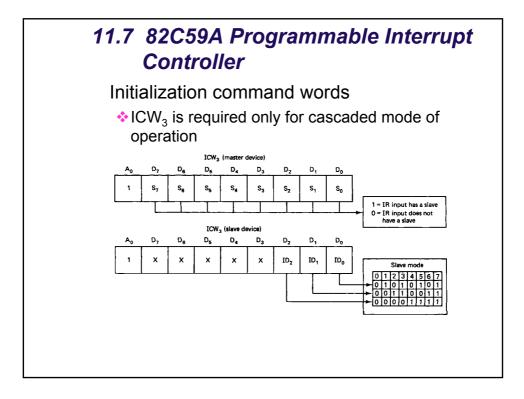

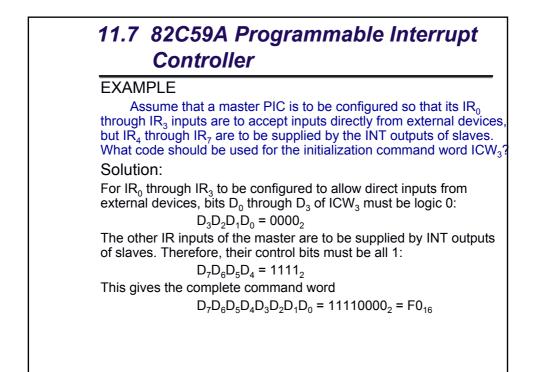

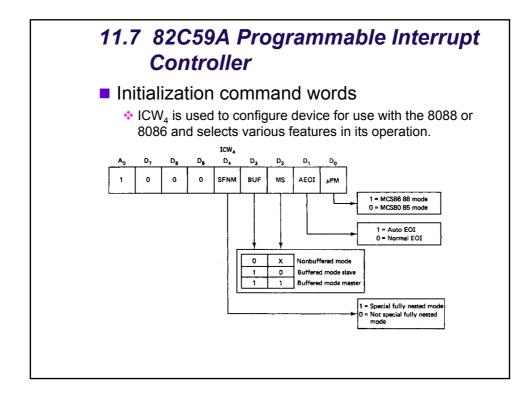

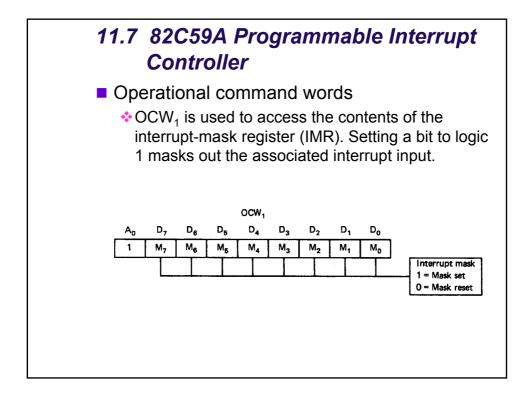

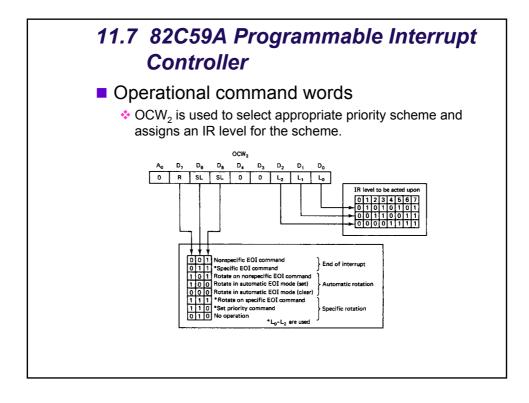

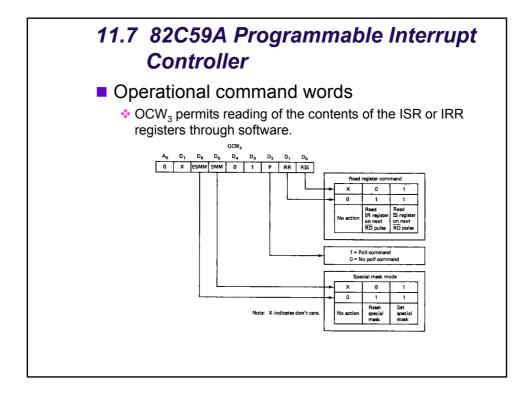

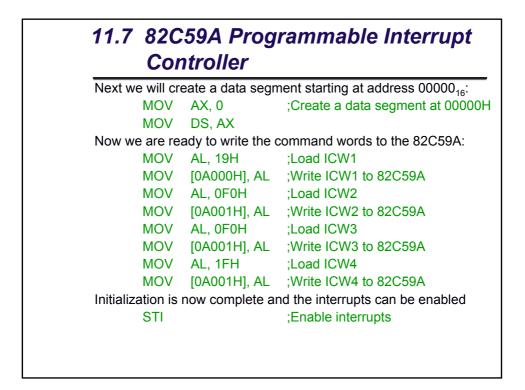

# **11.7 S2C59A Programmable Interrupt** Controller **Programming the 82C59A**\* Two types of command words are provided to program the 82C59A: the initialization command words (ICW) and the operational command words (OCW). \* ICW commands (ICW<sub>1</sub>, ICW<sub>2</sub>, ICW<sub>3</sub>, ICW<sub>4</sub>) are used to load the internal control registers of the 82C59A to define the basic configuration or mode in which it is used. \* The OCW commands (OCW<sub>1</sub>, OCW<sub>2</sub>, OCW<sub>3</sub>) permit the 8088 or 8086 microprocessor to initiate variations in the basic operating modes defined by the ICW commands. \* The MPU issues commands to the 82C59A by initiating output (I/O-mapped) or write (Memory-mapped) cycles.

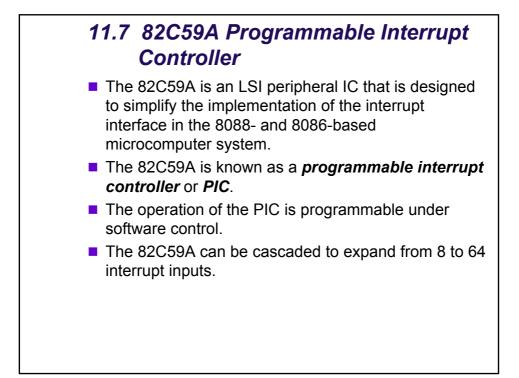

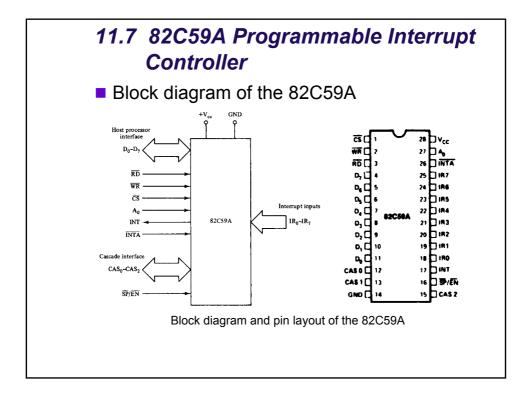

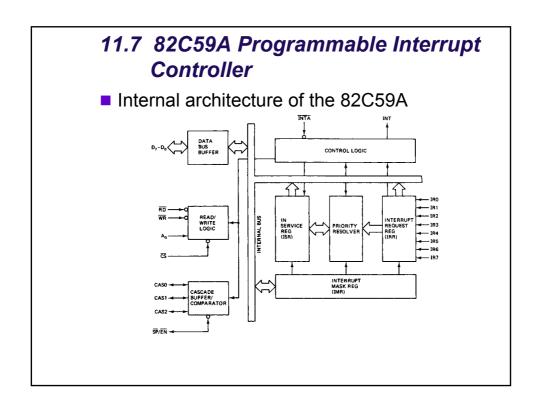

#### 11.7 82C59A Programmable Interrupt Controller

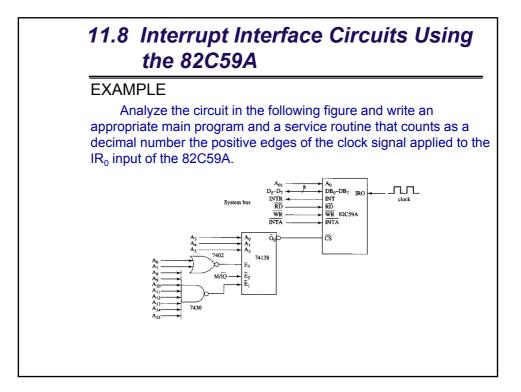

#### EXAMPLE

What should be the OCW<sub>1</sub> code if interrupt inputs  $IR_0$  through  $IR_3$  are to be masked and  $IR_4$  through  $IR_7$  are to be unmasked?

Solution:

For  $IR_{\rm 0}$  through  $IR_{\rm 3}$  to be masked, their corresponding bits in the mask register must be make logic 1:

$D_3D_2D_1D_0 = 1111_2$

On the other hand, for  $IR_4$  through  $IR_7$  to be unmasked,  $D_4$  through  $D_7$  must be logic 0:

$D_7 D_6 D_5 D_4 = 0000_2$

This gives the complete command word

$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0 = 00001111_2 = 0F_{16}$

## 11.7 82C59A Programmable Interrupt Controller

#### EXAMPLE

What OCW<sub>2</sub> must be issued to the 82C59A if the priority scheme rotate on nonspecific EOI command is to be selected?

Solution:

To enable the rotate on nonspecific EOI command priority scheme, bits  $D_7$  through  $D_5$  must be set to 101. Since a specific level does not have to be considered, the rest of the bits in the command word can be 0. This gives OCW<sub>2</sub> as

$D_7 D_6 D_5 D_4 D_3 D_2 D_1 D_0 = 10100000_2 = A0_{16}$

## 11.7 82C59A Programmable Interrupt Controller

#### EXAMPLE

Write a program that will initialize an 82C59A with the initialization command words  $ICW_1$ ,  $ICW_2$ ,  $ICW_3$  derived in the previous examples, and  $ICW_4$  is equal to  $1F_{16}$ . Assume that the 82C59A resides at address A000<sub>16</sub> in the memory address space.

#### Solution:

Since the 82C59A resides in the memory address space, we can use a series of move instructions to write the initialization command words into its registers. Note that the memory address for an ICW is  $A000_{16}$  if  $A_0 = 0$ , and it is  $A001_{16}$  if  $A_0 = 1$ . However, before doing this, we must first disable interrupts. This is done with the instruction

; Disable interrupts

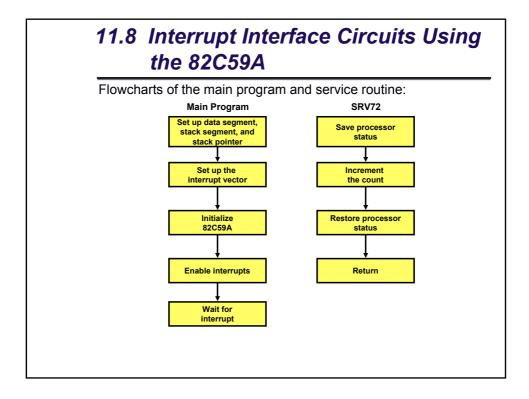

# 11.8 Interrupt Interface Circuits Using the 82C59A

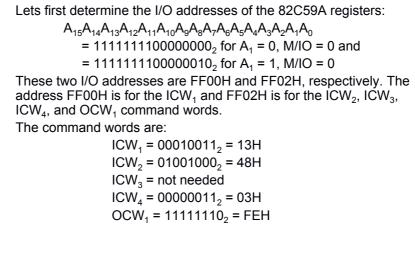

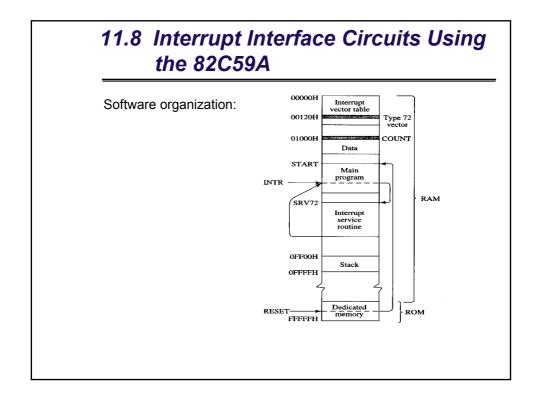

Solution:

| Program: |                     |                             |

|----------|---------------------|-----------------------------|

| ;MAIN PR | OGRAM               |                             |

| ,        | CLI                 | ;Start with interrupt disab |

| START:   | MOV AX, 0           | Extra segment at 00000      |

|          | MOV ES, AX          | -                           |

|          | MOV AX, 1000H       | ;Data segment at 01000      |

|          | MOV DS, AX          |                             |

|          | MOV AX, 0FF00H      | ;Stack segment at 0FF00     |

|          | MOV SS, AX          |                             |

|          | MOV SP, 100H        | ;Top of stack at 10000H     |

|          | MOV AX, OFFSET SRV7 | 2 ;Get offset for SRV72     |

|          | MOV [ES:120H], AX   | ;Set up the IP              |

|          | MOV AX, SEG SRV72   | ;Get CS for the service re  |

|          | MOV [ES:122H], AX   | ;Set up the CS              |

| MOV AL, 13H ;Ed<br>OUT DX, AL<br>MOV DX, 0FF02H ;IC'<br>MOV AL, 48H ;IC'<br>OUT DX, AL<br>MOV AL, 03H ;IC'                                     | W1 address                   |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| MOV AL, 13H ;Ed<br>OUT DX, AL<br>MOV DX, 0FF02H ;IC <sup>1</sup><br>MOV AL, 48H ;IC <sup>1</sup><br>OUT DX, AL<br>MOV AL, 03H ;IC <sup>1</sup> |                              |

| OUT DX, AL<br>MOV DX, 0FF02H ;IC<br>MOV AL, 48H ;IC<br>OUT DX, AL<br>MOV AL, 03H ;IC                                                           |                              |

| MOV AL, 48H ;IC'<br>OUT DX, AL<br>MOV AL, 03H ;IC'                                                                                             | lge trig input, single 8259A |

| OUT DX, AL<br>MOV AL, 03H ;IC                                                                                                                  | W2, ICW4, OCW1 address       |

| MOV AL, 03H ;IC                                                                                                                                | W2, type 72                  |

| OUT DX, AL                                                                                                                                     | W4, AEOI, nonbuf mode        |

| MOV AL, 0FEH ;OO<br>OUT DX, AL                                                                                                                 | CW1, mask all but IR0        |

|                                                                                                                                                | able the interrupts          |

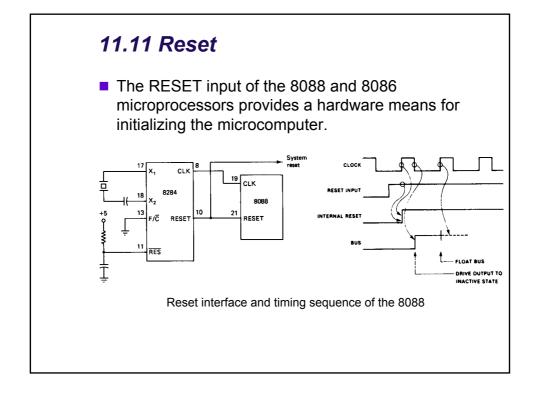

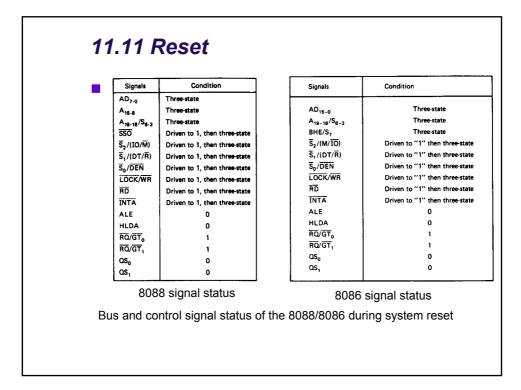

#### 11.11 Reset

When the MPU recognizes the RESET input, it initiates its internal initialization routine. At completion of initialization, the flags are all cleared, the registers are set to the values in the following table.

| CPU COMPONENT       | CONTENT |

|---------------------|---------|

| Flags               | Clear   |

| Instruction pointer | 0000H   |

| CS Register         | FFFFH   |

| DS Register         | 0000H   |

| SS Register         | 0000H   |

| ES Register         | 0000H   |

| Queue               | Empty   |

#### 11.11 Reset

- The external hardware interrupts are disabled after the initialization.

- Program execution begins at address FFFF0<sub>16</sub> after reset. This storage location contains an instruction that will cause a jump to the startup (boot-strap) program that is used to initialize the reset of the microcomputer system's resources, such as I/O ports, the interrupt flag, and data memory.

- After the system-level initialization is complete, another jump can be performed to the starting point of the microcomputer's operating system or application program.